为了减小匝间电容,可以选择介电常数较低的漆包线,也可以增大绕组匝间的距离,也可以用多槽的骨架进行分段绕制。从整体来看,匝间电容的影响相对于其他的分布电容来说,几乎可以忽略。

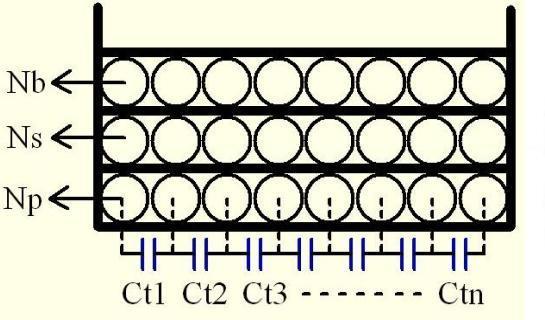

层间电容指的是变压器每个单独绕组各层之间的电容。需要有2个以上绕组层变压器才有。层间电容占变压器总分布电容的比例相当大,会加大MOSFET与次级Diode的电压应力,使EMC变差。

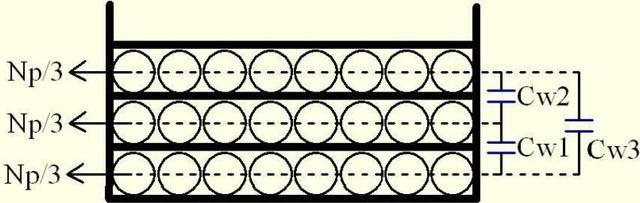

减小层间电容有多种方法,可以增大绕组层间距离,如采用三重绝缘线; 也可以选择绕线面积较宽的骨架; 还可以采用交叉堆叠绕法来降低层间电容。各种方法都有它的优缺点。

绕组间电容是共模的重要通路,所以对EMI很不利;一般减小方法是采用增加绝缘厚度,增加法拉第屏蔽层等方法来减少绕组间电容。

与屏蔽 实际电路都是由非理想元件组成的,在设计中可能会遇到许多预料不到的情况。在调试如图1所示的普通全桥电源时,输出不是料想中平稳的

与屏蔽 /

原理分析 实际电路都是由非理想元件组成的,在设计中可能会遇到许多预料不到的情况。在调试如图1所示的普通全桥电源时,输出不是料想中

的区别 /

的影响 /

对输出波形的影响 /

开源硬件-PMP30545.2-90V-265V 交流输入、多输出、非隔离反激式 PCB layout 设计

【Longan Pi 3H 开发板试用连载体验】给ChatGPT装上眼睛,并且还可以语音对线,项目开发环境搭建

星空全站 上一篇:大功率发生器电源用于工业零部件清洗 下一篇:基于摄动观测器的风电柔直并网系统控制方法研究